## Lab 3:

## Embedding VHDL code in a Xilinx Spartan 3E VI

$\underline{\text{Keywords}}\colon \text{LabVIEW}, \text{LabVIEW FPGA, Xilinx SPARTAN3E Starter Kit, } \\ \overline{\text{VHDL, Even Parity.}}$

## Introduction

Welcome to Lab3 in the serie of programming a SPARTAN3E Starter Kit by use of LabVIEW FPGA. These labs are created by Vincent Claes. If you encounter problems using this labs or want some advice/consultancy on LabVIEW and especially LabVIEW FPGA you can always contact the author.

These labs are free to use however to show respect to the author please email him when you use them with your contact details (feedback is also welcome).

Contact Information:

Vincent Claes

claesvincent@gmail.com

http://www.linkedin.com/in/vincentclaes

### Software Requirements:

- LabVIEW 8.5 or above

- LabVIEW 8.5 FPGA module

- XUP Spartan3E starter board: download for free from: https://lumen.ni.com/nicif/us/infolvfpgaxilsprtn/content.xhtml

#### Hardware Requirements:

- Xilinx Spartan3E Starter kit: http://www.xilinx.com/products/devkits/HW-SPAR3E-SK-US-G.htm

- User manual: <u>www.xilinx.com/support/documentation/boards\_and\_kits/ug23</u>

0.pdf

## Getting Started

When you want to use this labs you have to setup your board. This labs are written for the Xilinx SPARTAN3E Starter Kit so it is quite interesting to read the user manual of the board. Be sure to plug in the USB cable, plug in the Power cord and Switch the board on before starting the lab.

2008 Vincent Claes

# Step 1: Adding the FPGA I/O to your LabVIEW FPGA Project

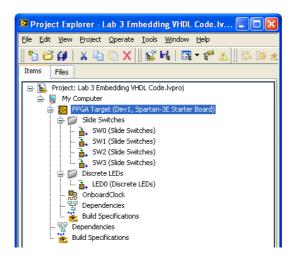

The first things we have skipped because it is the same as in Lab 1 & Lab 2. Try to setup yourself an LabVIEW FPGA project for the Xilinx Spartan3E starter board. When you reach the step where you have to add FPGA I/O to the FPGA Project add the "SWO", "SW1", "SW2", "SW3" and "LEDO" I/O pins.

In this lab we are going to create a parity checker. We will put "LEDO" of the Spartan3E Starter board on when the input of the checker system (by use of "SWO", "SW1", "SW2" and "SW3") has even bits.

## Step 2: Creating the VI.

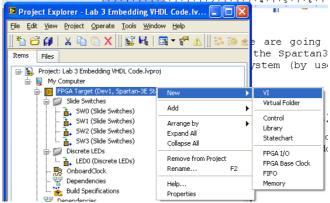

Do a "right mouse click" on the "FPGA Target" in the "Project Explorer". From the pull down menu select "New" >> "VI".

Name it "FPGA\_VI\_VHDL".

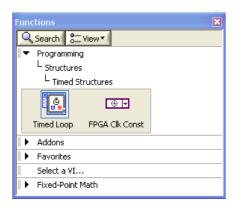

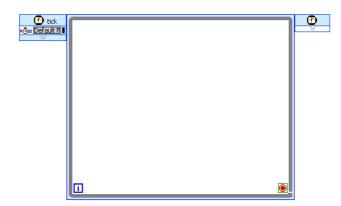

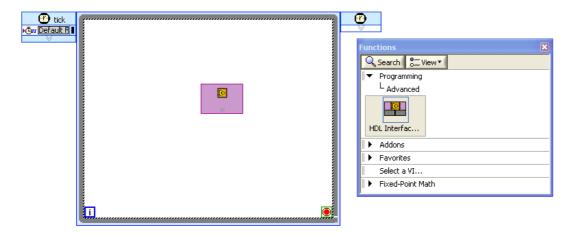

On the "block diagram" of this vi you have to put a "Timed Loop".

2008 Vincent Claes

In this "Timed Loop" you have to place a "HDL Interface Node".

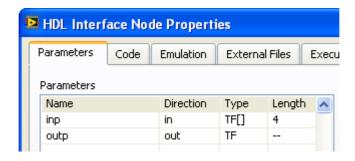

Now double click the "HDL Node"; you will get the following screen:

In the first screen try to add the following 2 parameters:

- "inp" with direction "in", type "TF[]" and Length "4".

- "outp" with direction "out" type "TF".

In the code screen replace "hdlnode" (name of the entity) to "even\_parity".

The field below "architecture implementation of even\_parity is" has to been filled with the following VHDL rule:

signal s1, s2, s3, s4, s5, s6, s7, s8: std\_logic;

The field below the VHDL keyword "begin" has to been filled with the following VHDL code:

This is a very simple VHDL program to show you how you can add VHDL code to your Spartan3E LabVIEW FPGA project.

In the tab "Execution Control" check the option "Single-Cycle Timed Loop Allowed" and click the "OK" button.

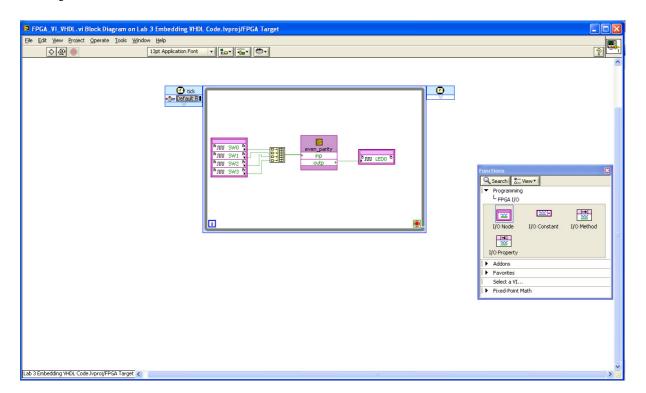

Now place two "FPGA I/O Node's" on the block diagram of your vi. Build an array with "SWO", "SW1", "SW2" and "SW3" as inputs. Connect the output of this "build array" function to the input of the "HDLNode" called "inp". Connect now "LEDO" to "outp" of the "HDLNode".

2008 Vincent Claes

# Step 3: Running the VI.

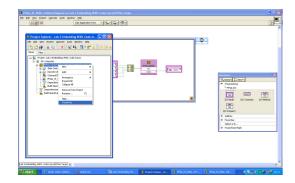

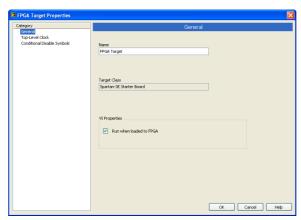

Now go to the "Project Explorer". Right mouse click on "FPGA Target" then select "Properties".

Be sure to check in this window "Run when loaded to FPGA" before compiling the vi.

Go back to "Project Explorer". Do a right mouse click on "FPGA\_VI\_VHDL". Select Compiler and let the LabVIEW FPGA code compile.

When the compilation completed go to "Project Explorer" and do a right mouse click on "FPGA\_VI\_VHDL" and select "Download VI to Flash Memory"

2008

When the download completed push the "reset" button on the Xilinx Spartan3E board and the application should run.

### Enjoy.

Vincent Claes XIOS Hogeschool Limburg Department of Industrial Sciences and Technology Universitaire Campus - Agoralaan - Gebouw H B-3590 Diepenbeek Belgium

### vincent.claes@xios.be

tel.: +32 11 26 00 39 fax: +32 11 26 00 54 mobile: +32 478 35 38 49

2008